UN MÉTODO Y UN DISPOSITIVO DE PROCESAMIENTO EN PARALELO DE INSTRUCCIONES DE PROGRAMA E INSTRUCCIONES DE TRAZA

-

Inventores/as:

- Antonio Da Silva Fariña

- Óscar Rodríguez Polo

- Agustín Martínez Hellín

- Pablo Parra Espada

- Sebastián Sánchez Prieto

-

Universidad Politécnica de Madrid

info

Universidad Politécnica de Madrid

Madrid, España

-

Universidad de Alcalá

info

Universidad de Alcalá

Alcalá de Henares, España

ES2697548A1 (24-01-2019)

ES2697548B2 (22-07-2020)

P201830266 (20-03-2018)

Laburpena

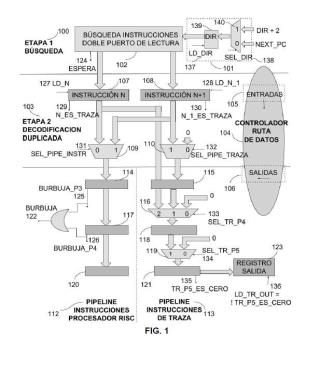

Método y dispositivo de sincronización y ejecución paralela de instrucciones de traza sobre un procesador RISC segmentado. La invención consiste en un dispositivo cuya estructura interna, basada en un procesador segmentado, permite eliminar la sobrecarga de tiempo de ejecución que introduce la instrumentación de código empleada para medir el tiempo de ejecución en el peor caso. Para ello el dispositivo utiliza un código de instrucción específico para la instrumentación, que es interpretado como la habilitación de traza de la instrucción que le precede, y que permite identificar unívocamente el momento de ejecución de dicha instrucción. El dispositivo propuesto ejecuta en paralelo, y de forma sincronizada, cada instrucción de traza con la instrucción a trazar que le precede, y condiciona dicha ejecución a que se complete, sin que se vea afectada por burbujas, la ejecución de la instrucción a trazar.